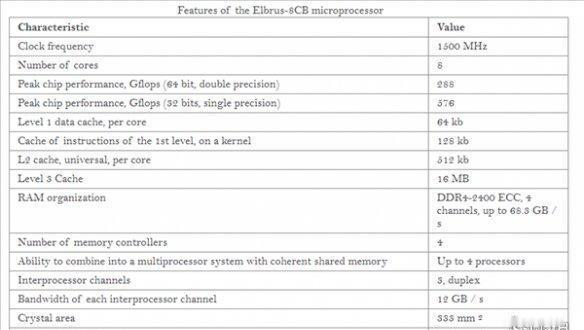

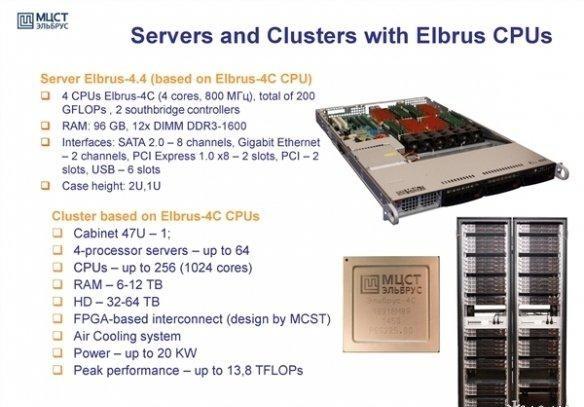

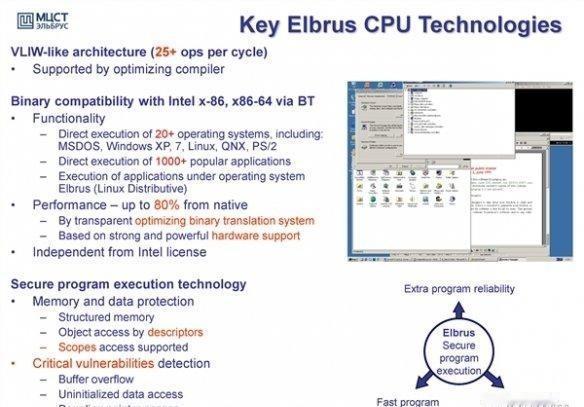

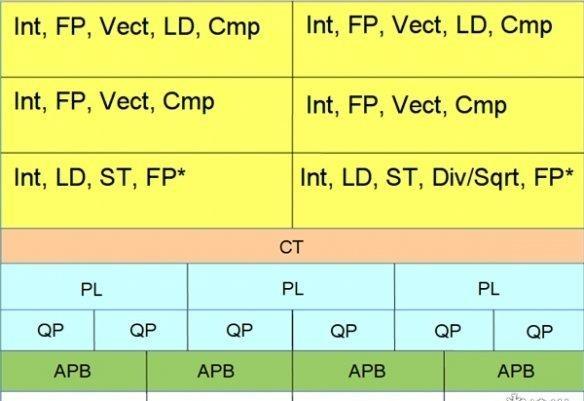

印度都造出CPU了!印度国产!28nm芯片!一步到位64位!双核1GHz!既不是X86架构,也不是ARM架构!印度的5G、汽车、工业设备、物联网、军事装备将用上这款印度国产芯片。印度这到底是怎么办到的啊? 印度中央先进计算发展中心在浦那开发DHRUV64处理器,这是印度微处理器开发计划的一部分。2025年12月15日推出,这款芯片采用28nm工艺,包含两个64位VEGA AS2161内核,运行频率1GHz。基于RISC-V开源指令集,实现了RV64IMAFD标准,支持整数、浮点和原子操作。处理器设计针对嵌入式系统,包含 superscalar 架构和乱序执行机制。印度电子与信息技术部资助该项目,旨在减少对外国芯片依赖。DHRUV64支持Linux内核和实时操作系统移植,但未公布详细性能基准数据。 DHRUV64的架构避免了X86和ARM的专利限制,使用开源RISC-V作为基础。这使得印度能快速进入处理器设计领域,而无需支付高额授权费。芯片包含约3000万逻辑门,适用于5G基站信号处理、汽车电子控制和物联网节点。相比中国龙芯系列,DHRUV64在工艺上落后3到5年,性能相当于早期龙芯水平。龙芯已实现小规模量产,而DHRUV64仍处于原型阶段。印度计划在本土设施生产,但28nm生产线预计2026年底建成。目前可能依赖海外代工厂,如台积电或三星。生态构建包括Zephyr和FreeRTOS支持,这些操作系统适合低功耗应用。 印度微处理器开发计划从2019年开始,DIR-V程序推动RISC-V生态建设。DHRUV64是该计划第三款芯片,前两款是VEGA系列单核处理器。中心与MosChip Technologies和Socionext合作,提供设计和验证支持。处理器接口采用AXI4标准,便于集成外围设备。中断控制器处理127个请求,确保实时响应。浮点单元符合IEEE 754规范,支持单双精度计算。印度政府强调这款芯片增强国家安全,适用于军事通信和工业自动化。相比俄罗斯埃尔布鲁斯系列,DHRUV64核心数较少,但采用更现代开源架构。俄罗斯处理器使用自主VLIW,DHRUV64则借助全球RISC-V社区资源。 DHRUV64的推出标志印度在半导体领域的进步,尽管参数不如国际主流产品。双核1GHz设计针对特定应用,如5G边缘计算和汽车传感器管理。印度半导体使命计划投资本土制造,目标到2030年建立完整供应链。目前,芯片测试在实验室完成,未来将扩展到商业部署。相比美国或中国产品,DHRUV64生态落后,需要更多软件适配。印度工程师利用开源工具加速开发,减少从零开始的成本。处理器支持哈佛架构,分开指令和数据缓存,提高效率。一级缓存32KB,二级512KB,这些配置适合中低端嵌入式场景。印度计划基于DHRUV64开发多核版本,提升性能覆盖更多领域。 俄罗斯埃尔布鲁斯处理器源于1970年代苏联项目,由列别捷夫研究所启动。埃尔布鲁斯-1于1978年完成,使用superscalar架构,早于西方类似技术。1980年代推出埃尔布鲁斯-2,支持多处理器配置,用于国防计算。到1992年生产约200台。1990年代,项目转向SPARC兼容设计,适应市场变化。莫斯科SPARC技术中心接手开发,推出埃尔布鲁斯-2000系列。2010年代,埃尔布鲁斯-4C采用28nm工艺,四核800MHz,支持DDR3内存。处理器兼容x86代码,通过二进制翻译运行Windows和Linux。 埃尔布鲁斯-8C于2014年原型完成,2016年开始量产。八核1.3GHz,28nm工艺,晶体管27.8亿。支持四通道DDR4-2400,带宽68.3GB/s。缓存结构包括每核64KB数据和128KB指令一级,512KB二级,共享16MB三级。处理器用于服务器和工作站,支持四路并行。互连带宽12GB/s,使用自主协议。编译器优化x86转换,效率达原生80%。埃尔布鲁斯系列强调不受外国授权限制,适用于安全敏感领域。俄罗斯政府推动其在军用系统应用,避免西方制裁影响。 2020年后,埃尔布鲁斯系列继续迭代。埃尔布鲁斯-8CB增加浮点性能,单精度576GFlops。集群配置使用多处理器节点,总性能13.8TFlops。2024年推出埃尔布鲁斯-2S3,针对嵌入式系统,支持Com Express标准。尺寸95mm x 95mm,集成图形和外围接口。俄罗斯Ruselectronics控股开发这些产品,强调本土供应链。埃尔布鲁斯-8S支持ccNUMA架构,便于扩展服务器集群。功耗控制在20千瓦内,使用风冷散热。处理器兼容多种操作系统,包括QNX和MS-DOS遗留代码。